Unità intera

Essa contiene due componenti, lo scheduler intero, e le unità di esecuzione intera.

Scheduler intero

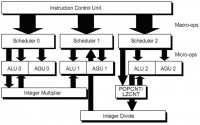

Esso è basato su un sistema di accodamento a 3 vie, chiamato anche reservation station (RS) che rifornisce le tre unità di esecuzione. Ognuna delle 3 code ha posto per 10 macro-op (8 nella precedente architettura Stars: code più lunghe significano maggiore possibilità di riordino delle istruzioni e quindi maggiori prestazioni) per un totale di 30 macro-op gestibili. Ogni RS suddivide la macro-op nelle sue componenti aritmetico logiche e di generazione indirizzo.

Unità di esecuzione intera

L’unità di esecuzione intera (IE) si compone di 3 elementi (pipeline 0, 1 e 2). Ogni elemento è composto da una unità aritmetico logica (ALU) e una unità di generazione indirizzo (AGU). La IE è organizzata in modo da collimare con le 3 pipeline di dispach delle macro-op della ICU, come visibile in figura.

Le macro-op sono spezzate in micro-op negli scheduler. Le micro-op sono eseguite quando i relativi operandi sono disponibili sia nei registri che nei bus dei risultati: in alcuni casi di istruzioni interdipendenti, non è necessario scrivere prima il risultato in un registro e poi leggerlo nel ciclo successivo, ma è possibile collegare le due istruzioni tramite uno dei bus di risultato disponibili.

Le micro-op provenienti da una singola macro-op possono essere eseguite fuori ordine ed inoltre una particolare pipeline intera può eseguire micro-op provenienti da macro-op diverse (una nella ALU e una nella AGU) contemporaneamente.

Ognuna delle tre ALU è in grado di eseguire istruzioni logiche, aritmetiche, funzioni condizionali, elaborazione dei flag di stato e calcolo dello stato di un salto.

Ognuna delle tre AGU è in grado di calcolare l’indirizzo lineare per un accesso in memoria o per l’istruzione LEA (che calcola l’indirizzo effettivo di un dato senza effettuare l’accesso in memoria. LEA sta infatti per Load Effective Address, ossia calcola e carica l’indirizzo effettivo).

E’ presente una unità per le letture e scritture in memoria, che accede effettivamente alla cache L1 dati, descritta più avanti (LSU, load and store unit).

Lo scheduler intero manda un segnale di completamento all’ICU per segnalare che una macro-op è stata eseguita. L’ICU ritirerà l’istruzione quando tutte le relative macro-op sono state eseguite.

Quasi tutte le operazioni intere possono essere eseguite indifferentemente dalle 3 ALU, con l’eccezione di moltiplicazione, divisione, LZCNT (leading zero count, ossia conteggio degli zero iniziali di un numero binario) e POPCNT (population count, ossia conteggio degli ‘1’ presenti in un numero binario).

Le moltiplicazioni sono gestite da un moltiplicatore pipelined, che è alimentato dalla pipeline 0. Per eseguire una moltiplicazione, però le pipeline 0 e 1 sono tenute bloccate simultaneamente, poiché il risultato di tutte le operazioni di moltiplicazione nella architettura x86 è a doppia precisione e richiede la specifica di due registri di destinazione. Durante l’esecuzione, le due pipeline 0 e 1 non possono essere usate se non per altre moltiplicazioni (perché il moltiplicatore è pipelined). Il moltiplicatore di Llano è stato ulteriormente migliorato rispetto alla precedente generazione di core Stars.

Analogamente la divisione usa le pipeline 1 e 2 e il divisore intero è alimentato dalla pipeline 2, poiché la divisione nella architettura x86 parte da dati a doppia precisione e fornisce risultato e resto in due registri separati. Durante l’esecuzione le due pipeline 1 e 2 non possono essere usate se non per altre divisioni (perché il divisore è pipelined).

Nella precedente architettura (core Stars) non esisteva un divisore hardware, ma la divisione era una lunga istruzione VectorPath che bloccava le pipeline 1 e 2 per tutto il tempo della sua lunga esecuzione (in Llano le divisioni sono anche il doppio più veloci) e non essendoci un divisore pipelined, poteva essere effettuata una divisione alla volta.

Le istruzioni LZCNT e POPCNT sono eseguite in una unità alimentata dalla pipeline 2 e finché è in esecuzione una di queste istruzioni la pipeline 2 non è utilizzabile da altre istruzioni diverse da queste due (perché l’unità è pipelined).

In definitiva una moltiplicazione blocca l’esecuzione di tutte le istruzioni non moltiplicative nelle pipeline 0 e 1 e anche di tutte le divisioni, che richiedono anche la pipeline 1 per funzionare. La divisione blocca l’esecuzione di tutte le istruzioni non di divisione nelle pipeline 1 e 2 e quindi anche le moltiplicazioni, che richiedono la pipeline 1, e le istruzioni LZCNT e POPCNT bloccano tutte le istruzioni che richiedono la pipeline 2 e quindi anche le divisioni.